# Red-Blue Pebbling with Multiple Processors: Time, Communication and Memory Trade-offs

Toni Böhnlein Computing Systems Lab, Huawei Zurich Research Center toni.boehnlein@huawei.com

Pál András Papp Computing Systems Lab, Huawei Zurich Research Center pal.andras.papp@huawei.com Albert-Jan N. Yzelman Computing Systems Lab, Huawei Zurich Research Center albertjan.yzelman@huawei.com

#### Abstract

The well-studied red-blue pebble game models the execution of an arbitrary computational DAG by a single processor over a two-level memory hierarchy. We present a natural generalization to a multiprocessor setting where each processor has its own limited fast memory, and all processors share unlimited slow memory. To our knowledge, this is the first thorough study that combines pebbling and DAG scheduling problems, capturing the computation of general workloads on multiple processors with memory constraints and communication costs. Our pebbling model enables us to analyze trade-offs between workload balancing, communication and memory limitations, and it captures real-world factors such as superlinear speedups due to parallelization.

Our results include upper and lower bounds on the pebbling cost, an analysis of a greedy pebbling strategy, and an extension of NP-hardness results for specific DAG classes from simpler models. For our main technical contribution, we show two inapproximability results that already hold for the long-standing problem of standard red-blue pebbling: (i) the optimal I/O cost cannot be approximated to any finite factor, and (ii) the optimal total cost (I/O+computation) can only be approximated to a limited constant factor, i.e., it does not allow for a polynomial-time approximation scheme. These results also carry over naturally to our multiprocessor pebbling model.

## 1 Introduction

The computational requirements of modern applications, ranging from scientific simulations to artificial intelligence, necessitate parallel data processing. However, developing parallel algorithms that efficiently divide (sub)tasks, manage memory, and organize communication between processors presents significant difficulties to computer scientists. One particular bottleneck for the performance of parallel computations is due to data locality, i.e., the memory of modern hardware features a hierarchical structure, and to process data, it has to be stored in the lowest layer. Since the layers' memory is limited in size, data movements between them (called I/O operations) are necessary and impact the execution time of computations significantly. The phenomenon becomes especially noticeable when dealing with tasks involving basic operations on large amounts of input data, e.g., the training of neural networks.

In this paper, we introduce a model offering improved insights into the challenges regarding I/O costs and limited memory in the context of parallel computing. Our focus is directed toward the efficient execution of a specific computation by several processors (rather than the design of a parallel algorithm tailored for a particular problem). We consider directed acyclic graphs (DAGs) as the model for a computation. The nodes correspond to single operations, while the directed edges express that the output data of a node is required as input for another node, enforcing precedence constraints on their order of execution. We are concerned with devising effective and efficient schedules for a given DAG and number of processors with limited working memory.

Hong and Kung [17] introduced the red-blue pebble game to study the I/O complexity of computations when executed by a *single* processor with a two-level memory hierarchy. The processor has *fast memory* (working memory) of limited capacity. Computing a node (and storing its output data in fast memory) requires that its predecessors' output data is stored in fast memory. To free up space in fast memory, I/O operations can transfer data to (and back from) *slow memory*, which has unlimited capacity.

In this model, available data is indicated by placing a *pebble* on the corresponding node. Data stored in fast memory is represented by a red pebble, and data in slow memory by a blue pebble. The game starts with an empty DAG. A red pebble can be placed on a node (i.e., computing the node) if all its predecessors have red pebbles on them. A red pebble can be placed on a node if it already has a blue pebble, and vice versa (I/O operations). Any pebble can be removed for free. The goal is to place pebbles on the sinks (outputs of the computation) while minimizing the number of I/O operations. The number of red pebbles may not exceed a given fast memory capacity at any time.

Red-blue pebbling studies trade-offs between I/O costs and memory size. In our paper, we extend this model to a setting where several processors compute in parallel, and communication is organized via shared memory; this allows us to study trade-offs between time, communication and memory size.

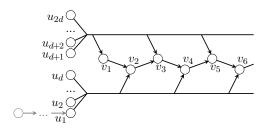

To familiarize ourselves with pebbling, consider the example DAG depicted in Figure 1. First, assume that we pebble it using only 3 red pebbles on a single processor. We may start by placing red pebbles on nodes  $v_1$  and  $v_2$ , which then permits us to place a red pebble on node  $v_3$ . The red pebbles on  $v_1$ and  $v_2$  are no longer needed and can be removed. Observe that to pebble node  $v_4$ , we again need all 3 red pebbles. Since  $v_3$  has an outgoing edge to node  $v_5$ , which we did not pebble yet, we place a blue pebble on  $v_3$  (casting our first I/O operation), and then remove the red pebble from  $v_3$ . Next,  $v_4$  (and its predecessors) can be pebbled analogously to  $v_3$ , leading to a configuration where we have a red pebble on  $v_4$  and a blue pebble on  $v_3$ . We use another I/O operation to put a red pebble back on  $v_3$ , since it has a blue pebble. Now, we can place a red pebble on node  $v_5$ , and then remove the red pebbles from  $v_3$  and  $v_4$ . Note that we pebbled the sub-graph in the dashed box with 2 I/O operations. Another I/O operation places a blue pebble on  $v_5$ . We pebble the subtree rooted  $v_6$  in an identical way to the one rooted at  $v_5$ . To finish, we bring a red pebble back to  $v_5$  with an I/O step, and then place a red pebble on  $v_7$ .

In contrast, consider pebbling the DAG with multiple processors for an intuitive description of our model. We use two processors  $p_1$  and  $p_2$  each having their own set of 3 red pebbles. To place a red pebble on a node, its predecessors require red pebbles of the *same* processor. We pebble the left and the right subtree of node  $v_7$  with red pebbles of  $p_1$  and  $p_2$ , respectively, using the strategy described above for a

Figure 1: A simple example DAG for pebbling.

single processor. All steps are executed in parallel, reducing both the compute and I/O operations by a factor 2. The result is a configuration with a red pebble of  $p_1$  and  $p_2$  on nodes  $v_5$  and  $v_6$ , respectively.

Recall that with one processor, we needed two I/O operations to convert the red pebble on  $v_5$  to blue and then back to red. In contrast, with two processors we need I/O operations to ensure that we have red pebbles of the same processor on  $v_5$  and  $v_6$ . The required communication between the processors is done via the shared memory (blue pebbles): We replace the red pebble of  $p_1$  on  $v_5$  by a blue pebble, and then the blue pebble by a red pebble of  $p_2$ . To finish the computation, we place a red pebble of  $p_2$  on  $v_7$ .

**Our Contribution.** We present the multiprocessor red-blue pebbling game (MPP), which is a natural generalization of red-blue pebbling. MPP essentially combines the areas of DAG pebbling problems (single-processor computation with limited memory) and DAG scheduling problems (multiprocessor computation, but with unlimited memory). The result is a simple yet expressive model that captures computational costs, I/O costs incurred by memory limitations, and inter-processor communication costs. Unlike earlier attempts to generalize red-blue pebbling, MPP naturally combines these aspects into a single cost function, allowing for a convenient study of the trade-offs between these factors. These trade-offs have been analyzed in detail for many concrete computations before (e.g., matrix multiplication [21, 20, 38]), but not for arbitrary computational DAGs.

We first discuss the basic properties of MPP, including simple bounds on the pebbling cost, NPhardness for specific DAG classes, and the analysis of a simple greedy approach. We also analyze how adding more processors (with the same, or reduced amount of fast memory) can affect the pebbling problem, i.e., how the optimal pebbling cost can change in the same DAG.

Then as our main technical result, we present two hardness results for approximating the optimal strategy in red-blue pebbling problems. Both of these proofs already apply to single-processor red-blue pebbling, thus presenting novel results for a problem that has been studied for several decades. Firstly, we show that the minimal number of I/O steps in a pebbling cannot be approximated in polynomial time to any finite multiplicative factor, or any additive  $n^{1-\varepsilon}$  term (for any  $\varepsilon > 0$ ), unless P=NP. Secondly, we show that the minimal total cost (including both I/O and computation steps) can only be approximated to a limited factor, i.e., there is a  $\delta > 0$  such that the optimum cannot be approximated to a  $(1+\delta)$  factor in polynomial time, unless P=NP; in other words, the problem is APX-hard, allowing no PTAS. Both of these results carry over naturally to our multiprocessor pebbling model.

## 2 Related Work

Pebble games are used to capture various aspects of computing. For instance, the standard (black) pebble game [9, 27] models general time-memory trade-offs, with results on achievable trade-offs [18, 22, 29] and the complexity of computing pebbling strategies [14, 10, 33, 2].

Hong and Kung [17] introduce the red-blue pebble game to study I/O complexity, and derive lower bounds based on a DAG partition technique. It is applied to specific computations in [13, 28]. Further bounds on I/O costs were derived with different methods in [19, 32, 15]. Other works [30, 31, 12] extend the red-blue pebble game to single and multiple processors over memory hierarchies. Kwasniewski et al. [20, 21] refine the technique of [17] and derive improved I/O lower bounds for special DAGs. The bounds are extended to a multiprocessor settings where the workload is perfectly balanced. In contrast to MPP, these works do not consider trade-offs between computation and I/O.

As for the complexity of computing optimal pebbling strategies, Demaine and Liu [11] show that

standard red-blue pebbling is PSPACE-complete, and propose variations that are shown NP-complete. NP-hardness for red-blue pebbling with computation costs is also shown in [6]. The work of [25] shows an inapproximability to a  $(2 - \varepsilon)$  factor, assuming the unique games conjecture. The work of [7] presents a bi-criteria approximation for the optimal I/O cost to a poly log(n) factor, provided that it is allowed to violate the memory bound by a poly log(n) factor.

Naturally, there are also several more realistic models that capture both parallelization and memory limitations, but these exhibit key differences from MPP. The work of [5, 8] studies the cost components (computation, different kinds of I/O) separately, mostly assuming that I/O steps cannot be parallelized. Other works assume simpler models regarding computation costs: they are not considered at all in [3], and are handled with artificial balance constraints in [34, 15]. Moreover, these models are primarily used for studying specific computations (e.g., Matrix multiplication, FFT) rather than arbitrary DAGs.

Valiant [37] introduces the bulk-synchronous parallel (BSP) computing model with explicit synchronisation, which was extended later [35, 24] to include data locality and communication via shared memory. The model was further generalized to capture multi-processor/core architectures with multi-level memory [38]. These models describe practical compute systems more closely, and also match our MPP model. There are also theoretical studies on DAG scheduling in BSP [26], but without memory restrictions.

## 3 Model Definition

Our model for a computation is a directed acyclic graph (DAG) G = (V, E). We use the notation n = |V| for the number of nodes. The in/out-degree of a node is the number of its incoming/outgoing edges. We call nodes with in/out-degree 0 the source/sink nodes. Let  $\Delta_{in}$  denote the highest in-degree in our DAG, i.e., the highest number of inputs to an operation in our computation; several previous works on pebbling assume that  $\Delta_{in}$  is small, e.g., a constant [11, 25]. Moreover, we denote the set of positive integers by  $\mathbb{Z}^+$ , and use the notation  $[a] = \{1, ..., a\}$ , for  $a \in \mathbb{Z}^+$ . Our goal is to execute a computational DAG on k processors, each having limited fast memory of size r, for parameters  $k, r \in \mathbb{Z}^+$ .

#### 3.1 Single Processor Red-Blue Pebbling

Before introducing our parallel model, we briefly recap the single-processor red-blue pebble game (SPP) [17], where we have a single processor with fast memory of size r and unlimited slow memory. Nodes with red pebbles on them (denoted  $R \subseteq V$ ) and nodes with blue pebbles on them (denoted  $B \subseteq V$ ) correspond to the output data that is currently saved in fast and slow memory, respectively. In order to pebble a DAG, the following rules can be applied:

- (R1-S) Place a red pebble on a node that has a blue pebble,

- (R2-S) Place a blue pebble on a node that has a red pebble,

- (R3-S) Place a red pebble on a node if all its predecessors have red pebbles on them,

- (R4-S) Remove a (red or blue) pebble.

The game starts with an empty DAG; rule (R3-S) allows us to place red pebbles on source nodes. A pebbling strategy is a sequence of the rules which places pebbles on the sink nodes in the end, while the number of red pebbles does not exceed r at any step. The I/O costs are the total number I/O operations, i.e., applications of rules (R1-S) or (R2-S). The goal is to pebble a DAG with minimum I/O costs. Most works on SPP analyze lower bounds on I/O cost for a given DAG and memory limit r.

Additional variations of SPP have also been proposed, aiming to simplify SPP, make it more realistic, or resolve the fact that this base SPP variant above is not even in NP, but rather PSPACE-complete. This is because the optimal pebbling sequence can be super-polynomially long in extreme cases, since repeatedly deleting and recomputing the same node incurs no cost. Notable SPP variants include:

- One-shot SPP: (R3-S) can be applied only once for each node [7],

- No-deletion SPP: (R4-S) is not allowed [11],

• SPP with computation costs: (R3-S) also incurs a small cost of  $\varepsilon$  [25, 6].

The first two variants feature somewhat artificial restrictions to prohibit the deletion and then recomputation of a node entirely. On the other hand, SPP with computation costs is more realistic, discouraging this in a natural way by ensuring that computation steps also incur some cost, as in practice. This last SPP variant is also the closest one our multiprocessor pebbling model.

We note that besides this, there are also smaller aspects of the definition that vary over different previous works: for instance, some assume that source nodes begin with a blue pebble, or that sink nodes specifically require a blue pebble in the end. For most proof constructions, these model variants can be reduced to each other with some simple tricks; we refer to [25] for a summary. Similarly, some works assume in rule (R1-S) that the new red pebble replaces the blue pebble, and in rule (R2-S) vice versa [25, 15]; our SPP-related claims also carry over easily to this variant.

#### 3.2 Multiple Processor Red-Blue Pebbling

We introduce the multiprocessor red-blue pebble game (MPP) which extends the red-blue pebble game to a setting where k processors compute a DAG G = (V, E) in parallel. Data stored in a processor's fast memory is represented by a red pebble of its *shade*, i.e., there are red pebbles of k different shades. The number of red pebbles of each shade is limited by r. The processors share unlimited slow memory that is used to (i) store data that cannot be kept in fast memory, and (ii) to communicate data between processors. Data available in the slow memory is represented by blue pebbles. Note that we assume that several pebbles of different shade/color can be placed on a node at the same time.

In our parallel version of the game, the rules allow multiple processors to simultaneously either transfer data between fast and slow memory, or compute nodes. More formally, define set  $R^j \subseteq V$  as the set of *red pebbles* of *shade* j, for  $j \in [k]$ , and set  $B \subseteq V$  as the set of *blue pebbles*. For  $m \in \mathbb{Z}^+$  such that  $m \leq k$ , we call an injective function  $f_m : [m] \to [k]$  a *shaded selection*, and extend the transition rules as follows:

- (R1-M) For a shaded selection  $f_m$  and vertices  $v_1, v_2, \ldots, v_m$  such that  $v_i \in R^{f_m(i)}$ , add  $v_i$  to B, for  $i \in [m]$ ,

- (R2-M) For a shaded selection  $f_m$  and vertices  $\{v_1, v_2, \ldots, v_m\} \subseteq B$ , add  $v_i$  to  $R^{f_m(i)}$ , for  $i \in [m]$ ,

- (R3-M) For a shaded selection  $f_m$  and vertices  $v_1, v_2, \ldots, v_m$  such that for all predecessors u of  $v_i$  we have  $u \in R^{f_m(i)}$ , for  $i \in [m]$ , add  $v_i$  to  $R^{f_m(i)}$ , for  $i \in [m]$ ,

- (R4-M) Remove a (red or blue) pebble.

A parallel version of (R4-M) could also be defined; we use this simpler version since this step incurs no cost in our model. Note that any single rule can place at most k pebbles, and that processors can be idle.

A configuration is a (k+1)-tuple  $C_i = (R_i^1, R_i^2, \ldots, R_i^k, B_i) \subseteq V^{k+1}$  defining red and blue pebbles placed on the DAG. A configuration  $C_i$  is valid if  $|R_i^j| \leq r$ , for  $j \in [k]$ , i.e., it respects the fast memory size. An initial configuration  $C_0$  sets  $R_0^j = \emptyset$ , for  $j \in [k]$ , and  $B_0 = \emptyset$ . Let  $S \subseteq V$  be the sink nodes. We say configuration  $C_i$  is terminal, if  $S \subseteq B_i \bigcup_{j=1}^k R_i^j$  holds. A pebbling strategy  $(C_0, C_1, \ldots, C_T)$ , for  $T \in \mathbb{Z}^+$ , is a sequence of valid configurations such that (i)  $C_i$  is obtained by applying a transition rule to  $C_{i-1}$ , for  $i \in [T]$ , and (ii)  $C_0$  and  $C_T$  are initial and terminal, respectively.

The pebbling strategy is represented equivalently by a sequence of transition rules  $(t_1, t_2, \ldots, t_T)$ , where  $t_i \in \{(\text{R1-M}), (\text{R2-M}), (\text{R3-M}), (\text{R4-M})\}$  such that  $C_i$  is the result of applying  $t_i$  to  $C_{i-1}$ , for  $i \in [T]$ . To assign costs to a pebbling strategy, we assign costs to each rule. Let  $g \in \mathbb{Z}^+$  be a parameter specifying the cost of an I/O step. We define the cost function for the transition rules as follows:

- $c(t_i) = g$  if  $t_i = (R1-M)$  or (R2-M),

- $c(t_i) = 1$  if  $t_i = (R3-M)$ ,

- $c(t_i) = 0$  if  $t_i = (R4-M)$ .

Then, the cost of a strategy  $C(t_1, t_2, \ldots, t_T) = \sum_{i=1}^T c(t_i)$  is the total costs of its rules. Given a DAG G and parameters  $k, r, g \in \mathbb{Z}^+$ , the goal of MPP is to find a minimum cost public strategy. We denote the cost of the optimum public strategy by OPT.

#### 3.3 Model Discussion

We first note that as in SPP, the rules of MPP allow for *recomputation*. Indeed, when I/O is expensive, it can sometimes be beneficial to compute the same node more than once; see Section 4 for an example.

Furthermore, the transition rules assume that the processors compute and access memory synchronously. This simplifies the analysis greatly, enabling us to formulate the cost function as a linear term of I/O and compute costs. However, in some practical settings, one processor may be computing while another one is accessing memory. This could be modelled by allowing each processor in a step to execute one of the SPP rules independently; however, assigning costs to a pebbling strategy then becomes an intricate matter. We expect that most of the general reasoning about pebbling strategies also carries over to such an asynchronous setting; it has been shown that the improvements from a non-synchronous schedule are limited to a factor 2 [26]. Synchronization of communication is also natural in some hardware architectures, and several parallel programming models, like BSP [37], also feature synchronization steps.

While parallel computing models typically study trade-offs between computation time and communication, SPP studies trade-offs between I/O costs and memory size. Combining these in MPP allows us to study the three-fold trade-off between computation time, communication, and memory size. The I/O steps in MPP can happen either due to (i) communicating data between processors, or (ii) saving data to slow memory to free up space in fast memory.

We note that several models in previous works are closely related to MPP; we discuss these in detail in Appendix A. For instance, [15] also outlines a generalization of SPP to multiple processors; however, in contrast to MPP, their work captures computation costs via an artificial balance constraint, which imposes heavy limitations on the model (see Appendix A.2). We also note that with  $r = \infty$  and minor adjustments, MPP also becomes equivalent to DAG scheduling in the BSP model [26]. This shows that with small variations, MPP is indeed a generalization of both SPP and DAG scheduling problems.

## 4 Fundamental Properties of MPP

**Straightforward bounds.** Similarly to SPP, if  $r \leq \Delta_{in}$ , then there can be no valid pebbling strategy, since a node of in-degree  $\Delta_{in}$  requires  $(\Delta_{in} + 1)$  red pebbles of the same shade to be computed:  $\Delta_{in}$  on its in-neighbors, and one more on the node itself. Thus we always implicitly assume  $r \geq \Delta_{in} + 1$ .

However, if  $r \ge \Delta_{in} + 1$ , there is indeed always a valid pebbling. Consider the nodes in any topological order. We can always select any processor p to compute the next node v, load all the (already computed) in-neighbors of v from slow memory to p (at a cost of at most  $\Delta_{in} \cdot g$ ), compute the node on p (at a cost of 1), save the value of v to slow memory (at a cost of g), and then remove the red pebbles from v and its in-neighbors (for free). This strategy incurs a cost of at most  $(\Delta_{in} + 1) \cdot g + 1$  for each node.

On the other hand, since each (R3-M) step can compute at most k nodes, the number of compute steps is at least  $\frac{n}{k}$ . This shows the following simple bounds for the optimal cost.

**Lemma 1.** For any instance of MPP, we have  $\frac{n}{k} \leq OPT \leq (g \cdot (\Delta_{in} + 1) + 1) \cdot n$ .

A simple example gadget. We briefly discuss a simple example, the *zipper gadget*, which highlights many vital aspects of pebbling problems, and different variants of it are used throughout our proofs. We only describe the gadget and these properties here on a high level, leaving the details to the corresponding proofs in the appendices. The gadget, shown in Figure 2, consists of two input groups  $S_1$ ,  $S_2$  of d nodes each, and a *main chain* of  $n_0$  nodes, with the input groups having edges to the main chain nodes in an alternating fashion. We typically have  $n_0 = n - O(1)$  to make  $S_1$  and  $S_2$  asymptotically irrelevant.

• The gadget was used in [25] to analyze trade-offs in SPP. E.g. for r=2d+2, we can always keep red pebbles on both  $S_1$  and  $S_2$ , and use the last 2 red pebbles to compute the main chain without any I/O steps. However, for r=d+2, we still need 2 red pebbles to compute along the main chain, so we repeatedly need to move the other d red pebbles between  $S_1$  and  $S_2$ , yielding a much higher cost.

Figure 2: Zipper gadget consisting of 2 input groups  $S_1 = \{u_1, u_2, \ldots, u_d\}$  and  $S_2 = \{u_{d+1}, \ldots, u_{2d}\}$ , and a main chain  $v_1, \ldots, v_{n_0}$ . The edges going from the input groups are combined into a single arrow for simplicity. The extension to discourage recomputation is only illustrated for  $u_1$  in gray.

- This example with r=d+2 also highlights the role of recomputation: we repeatedly need to move d red pebbles between  $S_1$  and  $S_2$ , and doing this with I/O steps (repeatedly loading from slow memory) incurs a cost of  $d \cdot g$  for each main chain node. However, since the nodes in  $S_1$  and  $S_2$  are sources, we can also simply compute them again with (R3-M) steps anytime, at a much lower cost of d per main chain node. To ensure that such a recomputation is always suboptimal, we can also attach a chain of length 2g in front of each node  $u_i$ : then recomputing  $u_i$  from a source node requires 2g + 1 compute steps, whereas saving  $u_i$  to slow memory and loading it back later costs at most 2g.

- Considering the gadget in MPP, if k=1 and r=d+2, we again need to keep moving the d red pebbles between  $S_1$  and  $S_2$ , which incurs a cost of  $(d \cdot g + 1)$  per main chain node. However, with k = 2processors and r=d+2, we can keep  $S_1$  and  $S_2$  in the fast memory of different processors, compute the main chain alternatingly, and only communicate these main chain nodes. This incurs a cost of  $(2 \cdot g + 1)$  per main chain node, thus describing a superlinear speedup for larger d values.

**NP-Hardness.** Regarding the complexity of MPP, it is not surprising that the problem is NP-hard, since it generalizes SPP. However, MPP is already NP-hard on rather simple subclasses of DAGs.

Lemma 2. MPP is already NP-hard on the following subclasses:

- 2-layer DAGs (where the longest path has length 1),

- *in-trees* (where every out-degree is at most 1).

The lemma follows from [26], where the same results are established for BSP scheduling; however, it requires some further work to adapt these proof constructions to MPP.

A Greedy Algorithm. It is also natural to wonder if we can obtain good solutions e.g. by following a greedy pebbling strategy. We can derive a naive upper bound on this approach, using the long known results that in DAG scheduling model memory limits or communication costs, any non-idle greedy strategy is a 2-approximation of the optimum [16]. Employing such a greedy approach for the computations, and assuming the worst-case strategy discussed for Lemma 1, we get the following bound.

**Lemma 3.** Any public where the compute steps follow a non-idle greedy schedule gives a  $2 \cdot (g \cdot (\Delta_{in} + 1) + 1)$ -factor approximation of the optimum.

Unsurprisingly, greedy strategies can also return rather bad solutions. In general, it is even non-trivial to precisely define a greedy strategy for MPP, since pebbling consist of various aspects. Here we make observations for a general class of greedy strategies: we only assume that processor p always picks the next node to compute as the yet uncomputed node with the largest number (or largest fraction) of in-neighbors having a red pebble of p. We show a lower bound for any such greedy strategy, regardless of how compute steps are parallelized, how ties are broken, or how I/O steps are applied to compute the chosen node.

**Lemma 4.** There exist DAGs where any such greedy pebbling algorithm is worse than the optimum

- by a  $\frac{1}{5} \cdot \Delta_{in} 1$  factor asymptotically (for any  $\Delta_{in} = O(1)$ ),

- by a  $\frac{2}{3} \cdot g + 1$  factor asymptotically (for any  $g \ge 2$ ).

Lower Bounds on Pebbling Costs. We now discuss how we can apply lower bounds on the number of required I/O steps from SPP to bound the optimum cost in MPP. The key insight is that a pebbling strategy for MPP can be implemented using a single processor (SPP) with fast memory of size  $r \cdot k$ . Specifically, each parallel rule can be simulated using k sequential rules.

**Lemma 5.** Let G be a DAG such that an SPP pebbling strategy with fast memory of size  $k \cdot r$  requires at least L steps of I/O, for some  $L \in \mathbb{Z}^+$ . Then, an MPP pebbling strategy with k processors, each having fast memory of size r, requires at least L/k steps of I/O.

**Corollary 6.** Let G be a DAG such that an SPP pebbling strategy with fast memory of size  $k \cdot r$  requires at least L steps of I/O, for some  $L \in \mathbb{Z}^+$ . Then, an MPP strategy with k processors and fast memory of size r each has cost of at least  $g \cdot L/k + n/k$ .

It follows that we can translate lower bounds for a single processor to k processors. Indeed, many previous works [17, 21] derive I/O lower bounds for specific computations in SPP, which are obtained utilizing a special DAG partition. For example, Hong and Kung [17] derive a lower bound of  $\frac{n \log n}{\log(rk)}$ on the number of required I/Os in SPP (with fast memory size  $r \cdot k$ ) for the *n*-point FFT DAG. The bound translates to a lower bound of  $\frac{n}{k} \cdot (g \cdot \frac{\log n}{\log(rk)} + 1)$  on the cost in MPP for the same DAG. Another well-studied computation is matrix-matrix multiplication. Kwasniewski et al. [21] improve the technique of [17] and derive a lower bound of  $\frac{2n^3}{\sqrt{rk}} + n^2$  in the single processor case, resulting in a lower bound of  $\frac{n}{k} \cdot (g \cdot (\frac{2n^2}{\sqrt{rk}} + n) + 1)$  on the costs of matrix-matrix multiplication in MPP. Finally, we show that there are instances where this lower bound is essentially tight.

**Lemma 7.** For any n, there is a DAG construction with  $OPT \leq g \cdot L/k + n/k + O(1)$  in MPP.

#### The Impact of More Processors: Trade-offs Between k, r and OPT 5

We next analyze how more available processors can affect the optimal pebbling strategy for a DAG, which captures fundamental trade-offs for parallel computing. For convenience, we compare the simplest case of 1 processor to k processors, but our proofs are easy to carry over to any k-fold increase in the number of processors. We use  $OPT^{(k)}$  as a short notation for the optimal pebbling cost with k processors.

There are two natural ways to do this comparison. Let  $r_0$  denote the amount of fast memory in the 1-processor case. One option is to compare this to a setting with k processors and  $r := \frac{r_0}{k}$  fast memory on each; we call this the *fair* comparison, as the total fast memory over all processors remains unchanged. Another option is to compare to a setting with k processors and simply  $r := r_0$  for each, i.e., all processors having the same fast memory  $r_0$  as before. This *practical* comparison is more relevant for applications, where computations are often parallelized by simply employing more processors of the same kind.

"Fair" Comparison. We first compare the case of 1 processor with  $r = r_0$ , to the case of k processors with  $r = \frac{r_0}{k}$ . This is an interesting setting: on the one hand, the k processors allow for parallelization of computations and I/O, but on the other hand, processors have less fast memory, possibly resulting in further I/O steps to save and reload data. We first show that the optimum cost can decrease by a factor k at most; intuitively, this is because in the fair case, any pebbling strategy with k processors can be transformed into a 1-processor schedule with at most k times larger cost. The bound is tight, as can be seen in e.g. a DAG with k independent chains of length  $\frac{n}{k}$ .

**Lemma 8.** In the fair case, we have  $\frac{OPT^{(k)}}{OPT^{(1)}} \ge \frac{1}{k}$ , and there are DAGs such that  $\frac{OPT^{(k)}}{OPT^{(1)}} = \frac{1}{k}$ .

With the same fast memory scattered over k processors, the optimum can also increase notably.

**Lemma 9.** In the fair case, there is a construction with

$$\frac{\textit{OPT}^{(k)}}{\textit{OPT}^{(1)}} \geq \frac{k-1}{k} \cdot g \cdot (\Delta_{in} - 1) + 1 - o(1).$$

Recall that  $OPT^{(1)} \ge n$  and  $OPT^{(k)} \le (g \cdot (\Delta_{in} + 1) + 1) \cdot n$ , so this bound is essentially tight for large k and  $\Delta_{in}$  values. Another construction shows that the optimum can also be non-monotonic in k.

**Lemma 10.** In the fair case, we can have e.g.  $OPT^{(2)} \leq OPT^{(1)}$  and  $OPT^{(2)} \leq OPT^{(4)}$ .

"Practical" Comparison. We now compare MPP with 1 and with k processors, with the processor(s) having the same  $r = r_0$  in both cases. Here the larger k value only comes with advantages, so the optimum can never increase; on the other hand, it can easily decrease as before, e.g., for k independent chains. What makes this setting more interesting is that the optimum can decrease by a factor larger than k; such a *superlinear speedup* is a well-known (and highly desired) phenomenon in real-world systems. To our knowledge, MPP is the first DAG scheduling or pebbling model that naturally captures this behavior.

**Lemma 11.** In the practical case, for any  $\varepsilon > 0$ , we can have  $\frac{OPT^{(1)}}{OPT^{(2)}} \ge \frac{\Delta_{in}-1}{2} - \varepsilon$ .

The proof idea has already been outlined in Section 4 with the zipper gadget. With the appropriate  $\Delta_{in}$ , the lemma can achieve a speedup of any constant factor, already for k = 2.

The number of I/O steps. We also briefly study the number of I/O steps separately: let  $OPT_{I/O}^{(k)}$  denote the number of steps (R1-M) and (R2-M) in the optimal pebbling with k processors. Our observations here hold for both the fair and the practical case.

Since k = 1 requires no communication, whereas k = 2 might, it is easy to construct a DAG where  $\mathsf{OPT}_{I/O}^{(1)} = 0$ , but  $\mathsf{OPT}_{I/O}^{(2)} = \Theta(n)$ . More surprisingly, we can also have a similar decrease in I/O, i.e., a DAG with  $\mathsf{OPT}_{I/O}^{(1)} = \Theta(n)$ , but  $\mathsf{OPT}_{I/O}^{(2)} = 0$ . Intuitively, this can happen when the computations can only be distributed in a very imbalanced way, so when we have 2 processors, it becomes more beneficial to do a lot of recomputations with one of the processors, instead of using I/O steps.

## 6 Inapproximability

Given the NP-hardness of MPP, a natural follow-up question is whether the optimum can be approximated to some factor in polynomial time. We show that MPP is also hard from this perspective.

**Theorem 12.** MPP is APX-hard: there is a constant  $\delta > 0$  such that no polynomial-time algorithm can approximate the optimum to a  $(1 + \delta)$  factor, unless P = NP.

We prove this property already for the simplest case of k = 1, i.e., SPP with computation costs. The proof can then easily be extended to any k value.

Lemma 13. SPP with computation costs is APX-hard.

Proof sketch. Our proof is motivated by a construction in [25], which reduces one-shot SPP to vertex cover on a graph of N nodes to show another property. However, this proof considers SPP, where (R3-S) compute steps are free, and hence the proof is rather careless with the number of nodes, using very large gadgets to ensure asymptotic behavior. As a result, the I/O cost is only  $\Theta(N) = o(n)$ . With computation costs adding up to at least n in SPP, this makes the I/O costs asymptotically irrelevant. Hence the reduction does not work directly for pebbling models with computation cost.

To adapt this idea, we substantially decrease the size of gadgets to ensure that n = O(N), and hence the I/O cost of any solution is in  $\Theta(N) = \Theta(n)$ . By design, in any reasonable solution, a specific part of this I/O cost is proportional to the size of a vertex cover in the underlying graph; as such, an approximation for the best pebbling could be transformed into an approximation of vertex cover. The main ingredients of the proof are as follows:

- we show how to modify the node gadgets in the construction of [25] to reduce their size to constant, thus ensuring that our construction has  $n = \Theta(N)$  altogether,

- we execute some further changes in the gadgets to avoid some other undesired properties, which could be ignored in the original proof of [25] due to their asymptotic analysis,

- we then show that in any reasonable pebbling, the I/O cost has a linear component that is proportional to the size of a vertex cover in the underlying graph.

Altogether, this modified construction allows for an L-reduction to the vertex cover problem in 3-regular graphs, which is known to be APX-hard [1]. This implies that it is already NP-hard to find a pebbling of cost at most  $(1 + \delta) \cdot \text{OPT}$  for an appropriate  $\delta > 0$ .

In general, the approximability of MPP is an intricate question, as the total cost is often dominated by computation costs, which are at least  $\frac{n}{k}$ . Thus, even if we have two solutions where I/O costs differ by a large factor, this can translate to only a negligible difference in total cost. To better capture these differences, we introduce an alternative cost metric.

**Definition 14.** Given an MPP pebbling strategy of cost C, its surplus cost is  $C - \frac{n}{k}$ .

Intuitively speaking, surplus cost ignores this unavoidable cost of  $\frac{n}{k}$ , and instead only measures "imperfections" in the pebbling, such as I/O steps, work imbalance between the processors, and recomputations. In terms of this new metric, finding a good solution is much more challenging: it is not possible to approximate the surplus cost in MPP to any finite factor. We again show this via proving an inapproximability result in standard one-shot SPP (i.e. minimizing I/O costs, with computations being free): we show that it is already NP-hard here to distinguish the cases when OPT = 0 and when  $OPT \ge n^{1-\varepsilon}$ , for any  $\varepsilon > 0$ .

**Theorem 15.** In one-shot SPP, it is NP-hard to approximate the optimum to any finite multiplicative factor, and to any additive  $n^{1-\varepsilon}$  term, in polynomial time (for any  $\varepsilon > 0$ ).

*Proof sketch.* The main part of our proof is to develop a DAG construction where it is already NP-hard to decide whether one-shot SPP has OPT = 0 or  $OPT \ge 1$ . After this, some technical steps allow for extending the same result to an optimum of either 0 or  $n^{1-\varepsilon}$ .

When looking for a solution of cost 0, pebbling becomes notably simpler: blue pebbles cannot be used at all, since (R1-S) and (R2-S) incur cost. The use of (R4-S) is also simple: without recomputation, a red pebble should be deleted exactly when all out-neighbors have been pebbled. As such, a pebbling is characterized by the order of the n computation steps.

We point out that pebbling with only (R3-S) and (R4-S) is essentially equivalent to one-shot *black pebbling*, which is long known to be NP-hard [33]; as such, the novelty of this part of our theorem is somewhat limited. However, [33] considers a slightly different variant of pebbling, where compute steps can also "slide" a pebble from an in-neighbor. It may also be possible to adapt the proof in [33] to our case with further work; instead, we present a novel, somewhat simpler reduction based on a different problem, and we also devise new gadgets that might be of independent interest for future works on pebbling.

Our construction is organized into consecutive chains of *level gadgets* that form *towers*. Intuitively, a pebbling strategy always needs to keep one level of each tower in fast memory, and it can 'proceed' to the next level, computing the nodes of the next level and deleting pebbles from the current level. There is no benefit to having partially pebbled levels in our DAG, and hence intuitively, each level can be considered a single entity in our analysis. To pebble the DAG correctly, we need to go through the towers of levels

Figure 3: Examples of consecutive levels. The 1st level (bottom row) always has size  $\ell = 5$ . The 2nd level (top row) has  $\ell' = 5$  on the left side,  $\ell' = 7$  in the middle, and  $\ell' = 3$  on the right.

Figure 4: High-level sketch of our construction: the main tower on the left, and node/edge gadgets on the right, with the level sizes and the dependency between incident node-edge pairs also shown.

in a carefully designed order, to ensure that the current set of levels never requires more than r pebbles altogether. The concrete level gadgets are shown in Figure 3, and discussed in detail in Appendix E.

Using these gadgets, we present a reduction from finding a clique of size q in a graph G'. Our DAG has a main tower, which is used to control the number of available pebbles at all times. We also add smaller tower gadgets for each node and edge of G', as illustrated in Figure 4. Furthermore, we draw edges between specific levels of the node and edge gadgets whenever a node is incident to an edge, and between specific levels of the main tower and all node and edge gadgets.

In the beginning, we can only pebble the 1st level of the main tower, then the first level of each node/edge gadget, and then the 2nd level of the main tower. Proceeding to the 3rd level of the main tower then frees up many pebbles; we can use these to proceed to the 2nd (and 3rd) level of node gadgets. However, due to  $b_2 > a$ , we can only move to the 3rd level of at most q node gadgets; otherwise, we would not have enough remaining pebbles to reach the 4th level of the main tower afterwards. Thus intuitively, any pebbling strategy corresponds to selecting at most q node gadgets.

The next levels of the main tower allow/require us to move to the 2nd level in edge gadgets. The 6th level again provides more free pebbles, so we can move to the 3rd (and then 4th) level in any edge gadget, provided that both of its incident nodes were chosen earlier. The next (7th) level then allows the fewest free pebbles: we can only proceed to this level if we reached the 4th level in at least  $\binom{q}{2}$  edge gadgets. This is only possible if we found a set of q nodes in G' that span  $\binom{q}{2}$  edges. Finally, after this point, the pebbling is easy to finish. Hence a pebbling of cost 0 exists if and only if G' has a clique of size q.

The theorem directly carries over to surplus cost in MPP: given the same DAG in MPP, a pebbling of cost 0 will translate to a surplus cost of 0, while a pebbling with  $n^{1-\varepsilon}$  I/O steps (or the same amount of recomputation) will translate to a surplus cost of at least  $n^{1-\varepsilon}$ .

**Corollary 16.** In MPP, it is NP-hard to approximate the optimum surplus cost to any finite multiplicative factor, and to any additive  $n^{1-\varepsilon}$  term, in polynomial time (for any  $\varepsilon > 0$ ).

## References

- Paola Alimonti and Viggo Kann. Some APX-completeness results for cubic graphs. Theoretical Computer Science, 237(1-2):123–134, 2000.

- [2] Per Austrin, Toniann Pitassi, and Yu Wu. Inapproximability of treewidth, one-shot pebbling, and related layout problems. In *International Workshop on Approximation Algorithms for Combinatorial Optimization*, pages 13–24. Springer, 2012.

- [3] Gianfranco Bilardi, Michele Scquizzato, and Francesco Silvestri. A lower bound technique for communication in BSP. ACM Transactions on Parallel Computing (TOPC), 4(3):1–27, 2018.

- [4] Rob H Bisseling. Parallel Scientific Computation: A Structured Approach Using BSP. Oxford University Press, USA, 2020.

- [5] Guy E Blelloch, Rezaul A Chowdhury, Phillip B Gibbons, Vijaya Ramachandran, Shimin Chen, and Michael Kozuch. Provably good multicore cache performance for divide-and-conquer algorithms. In Proceedings of the 19th annual ACM-SIAM Symposium on Discrete Algorithms, pages 501–510, 2008.

- [6] Jeremiah Blocki, Ling Ren, and Samson Zhou. Bandwidth-hard functions: Reductions and lower bounds. In Proceedings of the 2018 ACM SIGSAC Conference on Computer and Communications Security, pages 1820–1836, 2018.

- [7] Timothy Carpenter, Fabrice Rastello, P Sadayappan, and Anastasios Sidiropoulos. Brief announcement: Approximating the I/O complexity of one-shot red-blue pebbling. In *Proceedings of the 28th* ACM Symposium on Parallelism in Algorithms and Architectures, pages 161–163, 2016.

- [8] Rezaul Alam Chowdhury and Vijaya Ramachandran. Cache-efficient dynamic programming algorithms for multicores. In Proceedings of the 20th ACM Symposium on Parallelism in Algorithms and Architectures, pages 207–216, 2008.

- [9] Stephen A Cook. An observation on time-storage trade off. In Proceedings of the 5th annual ACM Symposium on Theory of Computing, pages 29–33, 1973.

- [10] Erik D Demaine and Quanquan C Liu. Inapproximability of the standard pebble game and hard to pebble graphs. In Workshop on Algorithms and Data Structures, pages 313–324. Springer, 2017.

- [11] Erik D Demaine and Quanquan C Liu. Red-blue pebble game: Complexity of computing the trade-off between cache size and memory transfers. In *Proceedings of the 30th ACM Symposium on Parallelism* in Algorithms and Architectures, pages 195–204, 2018.

- [12] Venmugil Elango, Fabrice Rastello, Louis-Noël Pouchet, Jagannathan Ramanujam, and Ponnuswamy Sadayappan. On characterizing the data movement complexity of computational dags for parallel execution. In *Proceedings of the 26th ACM Symposium on Parallelism in Algorithms and Architectures*, pages 296–306, 2014.

- [13] Venmugil Elango, Fabrice Rastello, Louis-Noël Pouchet, Jagannathan Ramanujam, and Ponnuswamy Sadayappan. On characterizing the data access complexity of programs. In Proceedings of the 42nd ACM SIGPLAN-SIGACT Symposium on Principles of Programming Languages, pages 567– 580, 2015.

- [14] John R Gilbert, Thomas Lengauer, and Robert Endre Tarjan. The pebbling problem is complete in polynomial space. In Proceedings of the 11th annual ACM Symposium on Theory of Computing, pages 237–248, 1979.

- [15] Niels Gleinig and Torsten Hoefler. The red-blue pebble game on trees and dags with large input. In International Colloquium on Structural Information and Communication Complexity, pages 135–153. Springer, 2022.

- [16] Ronald L. Graham. Bounds on multiprocessing timing anomalies. SIAM journal on Applied Mathematics, 17(2):416–429, 1969.

- [17] Jia-Wei Hong and Hsiang-Tsung Kung. I/O complexity: The red-blue pebble game. In Proceedings of the 13th ACM Symposium on Theory of Computing, pages 326–333, 1981.

- [18] John Hopcroft, Wolfgang Paul, and Leslie Valiant. On time versus space. Journal of the ACM (JACM), 24(2):332–337, 1977.

- [19] Saachi Jain and Matei Zaharia. Spectral lower bounds on the I/O complexity of computation graphs. In Proceedings of the 32nd ACM Symposium on Parallelism in Algorithms and Architectures, pages 329–338, 2020.

- [20] Grzegorz Kwasniewski, Tal Ben-Nun, Lukas Gianinazzi, Alexandru Calotoiu, Timo Schneider, Alexandros Nikolaos Ziogas, Maciej Besta, and Torsten Hoefler. Pebbles, graphs, and a pinch of combinatorics: Towards tight I/O lower bounds for statically analyzable programs. In Proceedings of the 33rd ACM Symposium on Parallelism in Algorithms and Architectures, pages 328–339, 2021.

- [21] Grzegorz Kwasniewski, Marko Kabić, Maciej Besta, Joost VandeVondele, Raffaele Solcà, and Torsten Hoefler. Red-blue pebbling revisited: near optimal parallel matrix-matrix multiplication. In Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis, pages 1–22, 2019.

- [22] Thomas Lengauer and Robert E Tarjan. Asymptotically tight bounds on time-space trade-offs in a pebble game. Journal of the ACM (JACM), 29(4):1087–1130, 1982.

- [23] Bill McColl. Mathematics, Models and Architectures, page 6–53. Cambridge University Press, 2021.

- [24] WF McColl and A Tiskin. Memory-efficient matrix computations in the BSP model. Algorithmica, 24(3-4):287–297, 1999.

- [25] Pál András Papp and Roger Wattenhofer. On the hardness of red-blue pebble games. In Proceedings of the 32nd ACM Symposium on Parallelism in Algorithms and Architectures, pages 419–429, 2020.

- [26] Pál András Papp, Georg Anegg, and A. N. Yzelman. DAG scheduling in the BSP model, 2023. arXiv preprint arXiv:2303.05989.

- [27] Michael S Paterson and Carl E Hewitt. Comparative schematology. In Record of the Project MAC conference on concurrent systems and parallel computation, pages 119–127, 1970.

- [28] Desh Ranjan, John Savage, and Mohammad Zubair. Upper and lower I/O bounds for pebbling r-pyramids. Journal of Discrete Algorithms, 14:2–12, 2012.

- [29] Rudiger Reischuk. Improved bounds on the problem of time-space trade-off in the pebble game. Journal of the ACM (JACM), 27(4):839–849, 1980.

- [30] John E Savage. Extending the Hong-Kung model to memory hierarchies. In International Computing and Combinatorics Conference, pages 270–281. Springer, 1995.

- [31] John E Savage and Mohammad Zubair. A unified model for multicore architectures. In *Proceedings* of the 1st international forum on next-generation multicore/manycore technologies, pages 1–12, 2008.

- [32] Jacob Scott, Olga Holtz, and Oded Schwartz. Matrix multiplication I/O-complexity by path routing. In Proceedings of the 27th ACM symposium on Parallelism in Algorithms and Architectures, pages 35–45, 2015.

- [33] Ravi Sethi. Complete register allocation problems. In Proceedings of the 5th ACM Symposium on Theory of Computing, pages 182–195, 1973.

- [34] Edgar Solomonik, Erin Carson, Nicholas Knight, and James Demmel. Trade-offs between synchronization, communication, and computation in parallel linear algebra computations. ACM Transactions on Parallel Computing (TOPC), 3(1):1–47, 2017.

- [35] Alexandre Tiskin. The bulk-synchronous parallel random access machine. *Theoretical Computer Science*, 196(1-2):109–130, 1998.

- [36] Luca Trevisan. Non-approximability results for optimization problems on bounded degree instances. In Proceedings of the 33rd ACM Symposium on Theory of Computing, pages 453–461, 2001.

- [37] Leslie G Valiant. A bridging model for parallel computation. Communications of the ACM, 33(8):103– 111, 1990.

- [38] Leslie G Valiant. A bridging model for multi-core computing. Journal of Computer and System Sciences, 77(1):154–166, 2011.

## A Further model discussion

### A.1 Other Model Variations

We briefly discuss several (minor) variations of MPP. Most of our results are easily adapted to these slightly different settings.

Similarly to SPP, there are multiple ways to define the initial and terminal configurations in MPP. For instance, instead of having source nodes that are freely computable with (R3-M), another SPP variant assumes that source nodes cannot be computed at all; instead, they have a blue pebble initially, and their data needs to be loaded with (R2-M). Similarly, instead of requiring all sink nodes to have a pebble of any color in the end, some SPP variants explicitly require that all sink nodes must have a blue pebble (i.e., sinks must all be saved to slow memory). Since the majority of our constructions have only O(1)sources and sinks, these changes only add a O(1) term to the cost of any pebbling.

Another alternative for MPP is to assume that processors cannot only exchange data via the slow memory, but also directly with each other, i.e., replacing a red pebble of  $p_1$  directly by a red pebble of  $p_2$ . For such an *MPP with direct sending*, we can replace the rules (R1-M) and (R2-M) by a new rule (R1-M)\* which allows us to take any set of different-colored pebbles (blue and/or different shades of red), and replace it by any other set of different-colored pebbles; we define this formally in Appendix A. An application of (R1-M)\* corresponds to a single communication step in a fully connected network topology between the k processors and the slow memory, with every participant sending and receiving at most one value. In the simplest case of  $r = \infty$ , this is essentially equivalent to DAG scheduling in the BSP model without latency [26]. This demonstrates that with minor variations, MPP is indeed a generalization of both SPP and DAG scheduling problems.

Formally, in the MPP variant with direct sending, for  $m \in \mathbb{Z}$  with  $m \leq k+1$ , let us define an extended shaded selection as a injective function  $f_m : [m] \to [k] \cup \{0\}$ . Instead of rules (R1-M) and (R2-M), we only have a single I/O rule, as follows:

(R1-M\*) Consider an extended shaded selections  $f_m$ , and vertices  $v_1, v_2, \ldots, v_m$  such that  $f_m$  satisfies  $v_i \in R^{f_m(i)}$  if  $f_m(i) \neq 0$  and  $v_i \in B$  if  $f_m(i) = 0$ , for all  $i \in [m]$ . For some other extended shaded selection  $f'_m$  with the same m, add  $v_i$  to  $R^{f'_m(i)}$  if  $f'_m(i) \neq 0$ , and add  $v_i$  to B if  $f'_m(i) = 0$ , for all  $i \in [m]$ .

The remaining components of the MPP definition remain unchanged, including rules (R3-M) and (R4-M). As before, rule (R3-M) incurs a cost of 1, while the new rule (R1-M)\* incurs a cost of g.

This modified I/O rule essentially assumes a fully connected (clique-like) communication network between the k processors and the slow memory, where in a single I/O step, any of the endpoints in this network (i.e., processor or slow memory) can send a data value to any other endpoint, but all endpoints can only send at most one and receive at most one piece of data. Several parallel computing models assume such an underlying communication setup, such as the communication cost function (named h-relation) in the BSP model [23, 4].

This variant is relevant because with direct sending, MPP essentially becomes a generalization of the DAG scheduling problem in BSP without latency, analyzed in [26]. This scheduling problem considers a more realistic model than previous works on DAG scheduling (already assuming e.g., communication costs that scale with data volume), but still makes some simplifications compared to practice (e.g., ignoring latency, assuming uniform node weights) for a simpler theoretical analysis. A BSP schedule in this model consists of computation and communication phases; however, these can all be split into separate steps for MPP with direct sending such that the total cost is unchanged. In particular, the cost  $s_{comp}$  of a computation phase is the maximum number of nodes executed on any processor; we can indeed split any such phase into  $s_{comp}$  distinct (R3-M) steps. The cost  $g \cdot s_{comm}$  of a communication phase is defined via *h*-relations; it is already discussed in [26] that any such phase can be split into  $s_{comm}$  distinct communication rounds, each of which are equivalent to a use of (R1-M)\*. For more details on this scheduling model, we refer the reader to [26].

Thus in the special case of  $r = \infty$ , MPP with direct sending is almost equivalent to a DAG scheduling problem. We note that the equivalence is not complete: even with  $r = \infty$ , an MPP strategy might still prefer to use blue pebbles. For a simple example, consider a pebbling strategy with two (R1-M)\* steps and three processors, where (i)  $p_1$  and  $p_2$  need to exchange a pair of node data in the first (R1-M)\* step, (ii)  $p_2$  and  $p_3$  need to exchange a pair of node data in the second (R1-M)\* step, and (iii)  $p_3$  needs to send another node v to  $p_1$  throughout this process. Without blue pebbles, we cannot send v in either of the steps, since  $p_1$  is already receiving in the first step, and  $p_3$  is already sending in the second. However, with blue pebbles also, we can move v from  $p_3$  to slow memory in the first (R1-M)\* step, and from slow memory to  $p_1$  in the second (R1-M)\* step. As such, the optimal cost in direct sending MPP might be lower than the optimum of the corresponding DAG scheduling problem.

It is also an interesting question how this direct sending variant differs from our original MPP problem. We discuss this in more detail in Appendix B.1 when analyzing how earlier NP-hardness results from DAG scheduling carry over to MPP.

We note that it would also be interesting to consider an MPP variant where a  $(R1-M)^*$  step is *added* to the set of rules, instead of replacing (R1-M) and (R2-M). Such a model would allow for a natural separation of I/O steps, based on whether they are motivated by memory limitations or by inter-processor communication. We leave it to future work to analyze such a model extension.

#### A.2 Comparison to constrained model

The closest previous work to our model is the extension of SPP to multiple processors in [15]. In this model, each processor can simultaneously execute a single one of the SPP rules, possibly different ones. The goal of the problem is to minimize the total number of applications of rules (R1-S) and (R2-S) in a pebbling; however, the strategy space is restricted to pebblings where the length of the sequence is minimal. This model differs from MPP in several ways:

- The model in [15] assumes each processor concurrently executes one of (R1-S)–(R4-S) in each step, hence implicitly assuming that all SPP steps take the same time.

- The model aims to minimize the total number of occurrences of (R1-S) and (R2-S) in a pebbling. This implicitly assumes that I/O on different processors cannot be parallelized.

- To motivate the parallelization of compute steps, the model has a further constraint: it only allows pebbling strategies that consist of the minimal possible number of steps. However, it is not even clear whether this condition can be verified in polynomial time.

Moreover, the strict constraint on the length of the pebbling can often exclude solutions with much fewer I/O steps; as such, while this is a promising preliminary model, we believe that our work is a simpler and more realistic way to capture red-blue pebbling in a parallel setting.

For completeness, we show a simple example where this artificially constrained model only allows pebblings with much higher I/O cost. Consider a DAG on 6 nodes: two chains of length 2 and 3, respectively, with their first node having an incoming edge from a common source node. Assume k = 2and  $r \ge 6$ . If executed on a single processor, this sequence consists of 6 compute steps, with no I/O operations. On the other hand, the pebbling sequence of minimal length also uses I/O steps:  $p_1$  computes the source node, then sends it to slow memory via (R1-S). For the next 3 steps,  $p_1$  computes the chain of length 3, while  $p_2$  loads the source node from slow memory, and computes the chain of length 2. This pebbling sequence consists of only 5 steps, but has 2 I/O steps. If g is large (i.e., in any model that accounts for the fact that communication steps are much more costly in practice than compute steps), this is a significantly more costly strategy than the one with 6 compute steps. However, since the constrained model only allows sequences of minimal length, it is restricted to this more expensive solution.

We can easily construct similar examples on arbitrary large DAGs: consider two sets A and B of m nodes each, and two sets  $C_1$  and  $C_2$  of (2m+1) and (m+1) nodes, respectively, with  $(u, v) \in E$  for all  $u \in A$ ,  $v \in C_1 \cup C_2$ . If A,  $C_1$  and  $C_2$  are all computed on  $p_1$  (and B on  $p_2$ ), we get a pebbling sequence of 4m + 2 compute steps, without any I/O. However, if A and  $C_1$  are computed on  $p_1$ , while B and  $C_2$ on  $p_2$ , then we need only need 4m + 1 steps in our sequence, but we have 2m I/O operations (of sending the data of A to  $p_2$ ).

## **B** Proofs for properties in Section 4

#### B.1 NP-hardness: proof of Lemma 2

We now discuss how to apply the constructions in [26] to show that MPP is already NP-hard on 2-layer DAGs and in-trees. Note that the work of [26] considers DAG scheduling in the BSP model. As discussed in Appendix A, this is equivalent to the direct sending variant of MPP with  $r = \infty$  and the modification that we cannot use blue pebbles at all. As such, for the rest of this section, we will understand the BSP scheduling problem to refer to this direct sending MPP problem variant with  $r = \infty$  and no use of blue pebbles.

### B.1.1 Original MPP vs. Direct Sending

Consider the BSP scheduling problem with some parameter g, and our original MPP problem with  $g' = \frac{g}{2}$ and  $r = \infty$ . At first glance, it might seem that these two settings are equivalent, since any direct sending (i.e., (R1-M)\* communication step) in BSP scheduling can be replaced by a consecutive (R1-M) and (R2-M) step, by sending the same (at most k) data values first all to slow memory, then to the corresponding processors. Indeed, the existence of a BSP schedule of cost C implies that there also exists an MPP pebbling with the same cost C. However, the reverse is not true: the optimum cost in MPP pebbling can be lower than in the corresponding scheduling problem.

Intuitively, there are two ways in which MPP with  $g' = \frac{g}{2}$  and  $r = \infty$  is a more flexible model than BSP scheduling with g. On the one hand, splitting each communication step into an (R1-M) and (R2-M) part allows for efficient broadcast operations: if a node v has to be sent from processor  $p_1$  to all the remaining (k-1) processors, then this can be achieved in a single pair of (R1-M) and (R2-M) steps in MPP (at a cost of g' + g' = g), whereas it takes (k-1) communication steps in BSP scheduling (and a cost of  $(k-1) \cdot g$ ).

On the other hand, the splitting of communication steps into an (R1-M) and an (R2-M) part also allows us to better parallelize communications occasionally. For instance, assume that we want to send a node  $v_1$  from processor  $p_1$  to  $p_3$  at some point in time  $t_1$ , and another node  $v_2$  from  $p_2$  to  $p_1$  at a later time  $t_2$ , and finally, there is a third data  $v_3$  to be sent from  $p_2$  to  $p_3$ , which can be sent either at  $t_1$  or  $t_2$ (i.e.,  $v_3$  is computed on  $p_2$  before  $t_1$ , but only required on  $p_3$  after  $t_2$ ). In BSP scheduling, the transfer of  $v_3$  cannot be parallelized with either of the other operations, since  $p_3$  is already receiving a value at  $t_1$ , and  $p_2$  is already sending a value at  $t_2$ ; as such, it requires a separate communication step, and hence the total cost of the communication steps is  $3 \cdot g$ . On the other hand, in MPP, we can already move  $v_3$  to slow memory in the (R1-M) step at  $t_1$  (together with  $v_1$ ), and load it from slow memory in the (R2-M) step at  $t_2$  (together with  $v_2$ ), since  $p_2$  is not yet sending a value at  $t_1$ , and  $p_3$  is not yet receiving a value at  $t_2$ . The total cost is then only  $4 \cdot g' = 2 \cdot g$ .

As such, in order to show that the NP-hardness proofs for BSP scheduling from [26] also carry over to MPP, we need to show that the differences above do not affect the optimum pebbling cost in the specific constructions, and hence an MPP scheduling of a given cost C exists if and only if a BSP scheduling of the same cost exists.

#### B.1.2 2-layer DAGs

For 2-layer DAGs, we use the fact that the proof reduction in [26] only has k = 2; we show that for this case, the optimum costs in the corresponding BSP scheduling and MPP problems are always identical.

We show that any MPP pebbling can be turned into a BSP schedule of at most the same cost (the reverse was already shown above). Note that for k = 2 and  $r = \infty$ , all data values sent from  $p_1$  are communicated in order to be received by  $p_2$ , and all data values sent from  $p_2$  are communicated in order to be received by  $p_1$ . We assume that our starting MPP schedule is reasonable, i.e., it does not send values to slow memory that are not loaded later by the other processor, or does not send/load the same value from/to a processor multiple times; otherwise, we can remove the corresponding unnecessary steps from the pebbling without increasing the cost.

We will consider the (R1-M) and (R2-M) operations in the MPP solution in order, and replace them by (R1-M)\* steps without ever increasing the total cost. In particular, consider the first (R2-M) step in the pebbling that has not been converted yet. First let us assume that this step only loads a single value from slow memory (assume, w.l.o.g., that this is a node  $v_1$  sent from  $p_1$  to  $p_2$ ). Let us find the preceding (R1-M) step that saves  $v_1$  from  $p_1$  to slow memory. If this (R1-M) step only transfers  $v_1$ , then we can combine the corresponding (R1-M) and (R2-M) into a (R1-M)\* step, sending  $v_1$  from  $p_1$  to  $p_2$ , at the original time of the (R2-M) step, with the cost remaining unchanged (g' + g' = g). If, on the other hand, the (R1-M) step saving  $v_1$  also transfers another value  $v_2$  from  $p_2$  to slow memory, then we can merge the two operations into a BSP communication step that, sends  $v_1$  from  $p_1$  to  $p_2$  and  $v_2$  from  $p_2$  to  $p_1$ , at the original time of the (R2-M) step, again at the same cost. Note that in our original pebbling,  $v_2$ was loaded to  $p_1$  from slow memory at a later point in time; we can now remove  $v_2$  from this (R2-M) operation, possibly deleting the entire operation if no other data value was loaded to  $p_2$  in the same step.

On the other hand, assume that the first unprocessed (R2-M) step loads both  $v_1$  (originally sent from  $p_1$ ) to  $p_2$  and  $v_2$  (originally sent from  $p_2$ ) to  $p_1$ . In this case, there are two corresponding (R1-M) steps earlier that send  $v_1$  and  $v_2$  to slow memory. If these two are in fact the same (R1-M) step, then we can simply combine the (R1-M) and (R2-M) step into a (R1-M)\* step of the same cost, at the original time of the (R2-M) step. Otherwise, if one or both of these (R1-M) steps also save other value(s) to slow memory besides  $v_1$  and  $v_2$ , we can still create the same (R1-M)\* step sending  $v_1$  from  $p_1$  to  $p_2$  and  $v_2$  from  $p_2$  to  $p_1$ , and merge the saving of these possible other values to slow memory into a new (R1-M) step. Note that besides  $v_1$ , an (R1-M) step could only send a value from  $p_2$ , and besides  $v_2$ , an (R1-M) step could only send a value from  $p_2$ , and besides  $v_2$ , an (R1-M) step could only send a value from  $p_2$ , and besides  $v_1$  in this process, and the newly merged (R1-M) step still results in a valid pebbling if placed at the time of the later one of the original two (R1-M) steps.

As such, the conversion shows that there exists a direct sending pebbling strategy with at most the same communication cost as our standard MPP pebbling, and hence the two problems have equal optimum values. As a result, the reduction of [26] for NP-hardness also carries over to MPP.

#### B.1.3 In-trees

For in-trees, one needs to delve into the concrete proof details in [26] to show that the same reduction holds for MPP. We outline the minor differences required in the proof when applied to MPP; for more details and context, we refer the reader to the detailed proof in [26].

On a high level, the reduction has an allowed cost of  $\frac{n}{k} + m_0 \cdot g$  for some parameter  $m_0$ , which immediately implies that we can have at most  $m_0$  communication steps. Furthermore, there is a sink node  $u_0$ ; assume w.l.o.g. that it is assigned to processor  $p_0$ . This  $u_0$  has  $\frac{n}{k} - 1$  in-neighbors, and also  $m_0$ further incoming edges from nodes  $u_i$  in other gadgets; one can show that all of these nodes  $u_i$  must all be assigned to a different processor than  $p_0$ , otherwise we exceed the allowed cost. This means that we need to send  $m_0$  distinct data values from other processors to  $p_0$ ; in BSP scheduling, this requires  $m_0$ separate communication steps. Since the allowed cost is  $\frac{n}{k} + m_0 \cdot g$ , this already implies that the cost of computation steps must sum up to  $\frac{n}{k}$ , and the cost of communication steps must sum up to  $m_0 \cdot g$ . The rest of the analysis is based on these observations.

In contrast to this, in MPP with  $g' = \frac{g}{2}$ , the same setting does not immediately imply that these

communication steps require all our budget for communication. In particular, loading the  $m_0$  values from slow memory to  $p_0$  still must happen in  $m_0$  separate (R2-M) steps, and hence at a cost of  $m_0 \cdot g'$ . However, the  $m_0$  values may, in fact, be saved to slow memory in a parallel fashion from the other (k-1)processors, if the  $u_i$  are distributed in a balanced way among them; instead of  $m_0 \cdot g'$ , this would only incur a cost of  $\frac{m_0}{k-1} \cdot g'$ . As such, this setting would allow us to have extra computation or communication steps compared to BSP scheduling, without violating the cost limit.

Hence in order to show that the communication steps must still sum up to a cost of  $2 \cdot m_0 \cdot g'$ , we need to consider further proof details. In particular, to enforce a timing on the communication steps, the construction has a critical path of length  $\frac{n}{k}$ ; if we only have  $\frac{n}{k}$  computation steps to fit into the allowed cost, then this implies that the *j*-th node of this path must always be computed in the *j*-th computation step. In MPP, we now only have a slack of  $s := (m_0 - \frac{m_0}{k-1}) \cdot g'$ , i.e., we have so far only shown an upper bound of  $\frac{n}{k} + s$  on the number of allowed computation steps, so with a similar approach, we can only claim that the *j*-th node of the path must be computed in the (j + s)-th computation step at the latest.

The key observation for adapting the proof to MPP is that such a small additive term s does not affect the induction step in the proof that establishes the timing of the communication steps, since  $s \leq m_0 \cdot q'$ , i.e., a much smaller magnitude than the size of gadgets in the construction. In particular, for the first node of the critical path that has a gadget attached (and then for each subsequent such node in the induction), it still holds that it has far too many predecessors to compute on a single processor in the first (j+s) computation steps. Hence as in the original proof, a communication step is required within these gadgets to share the workload, which in MPP means that we need to have both a (R1-M) and a (R2-M) step. However, in these first (j + s) compute steps, we still do not have enough remaining computations to finish more than one of the gadgets with  $u_i$  that have an edge to the sink  $u_0$ . As such, any valid pebbling has at least one (R1-M) and (R2-M) step before the (j + s)-th compute step, and these must transfer exactly one of the data values  $u_i$  to slow memory and then to  $p_0$ . The induction follows for the next splitting points of the critical path in a similar way, as in the original proof: even with the potential s extra compute steps, the remaining compute steps until the given computation deadline are not enough for the remaining predecessors, and hence another communication (pair of (R1-M) and (R2-M) steps) is required. This (R1-M) can once again only upload a single one of the values  $u_i$  to slow memory, since the compute steps are not enough to compute more than one of the gadgets connected to  $u_0$ . Altogether, this induction shows that any valid pebbling must have  $m_0$  distinct (R1-M) steps, and save a single one of the  $u_i$  values to slow memory in each of them.

This implies that any valid pebbling will have a total cost of at least  $m_0 \cdot 2 \cdot g' = m_0 \cdot g$  for communication, and hence a cost of exactly  $\frac{n}{k}$  for computation steps; from here, the proof becomes identical to that in the original setting. For simplicity, we can even delay all the (R1-M) steps in MPP to immediately before the succeeding (R2-M); the pebbling still remains valid, and the resulting sequence now becomes essentially identical to the corresponding BSP schedule, since the (R1-M)-(R2-M) pairs can be converted into (R1-M)\* steps.

#### B.2 Greedy approach: proofs of Lemmas 3 and 4

The proof of the upper bounds on the greedy algorithm were already outlined before. Recall that these follow from a fundamental result in DAG scheduling, which states that in the simplest DAG scheduling model (which is equivalent to MPP with g=0 and  $r=\infty$ ), any non-idle greedy strategy (i.e., where no processor remains idle when there are computable nodes) is a 2-approximation [16].

Proof of Lemma 3. Let  $L_0$  denote the minimal number of compute steps required in any pebbling; clearly  $L_0 \leq \text{OPT}$ . As noted above, a non-idle greedy strategy has at most  $2 \cdot L_0$  compute steps. Using the worst-case I/O strategy discussed for Lemma 1 (always saving every node to, and always loading every in-neighbor from slow memory) adds at most  $(\Delta_{in} + 1)$  I/O steps to each compute step, and hence its total cost is at most  $2 \cdot L_0 \cdot (g \cdot (\Delta_{in} + 1) + 1)$ .

We now move on to discuss the constructions to show Lemma 4, i.e., the lower bounds on the suboptimality of the greedy pebbling approach.

Recall that our greedy pebbling strategy is not entirely defined; instead, we consider a class of greedy strategies, and our lower bound holds for any strategy from this class. In the first steps, each of the processors selects a distinct source node in the DAG, and computes it concurrently (our constructions both have k = 2 and exactly two source nodes, so with this all sources are already computed). Then in every subsequent step, we consider the set of *ready nodes*, i.e., nodes v such that all the in-neighbors of v have already been computed before on some processor, but v has not yet been computed. Each processor  $p_i$  selects a *next-goal node* from among these ready nodes: according to the greedy rule, this could be either the ready node with the highest number of red pebbles of  $p_i$  on its in-neighbors, or alternatively, the highest ratio of red pebbles on in-neighbors to the number of in-neighbors (at the point of computing the previous next-goal node of  $p_i$ ). In case if there are multiple nodes tied for next-goal node, the processors can break ties arbitrarily; if multiple processors would select the same node, we can assign this node to one of these processors (with arbitrary tie-breaking), and the remaining processors can then follow the same rule to choose from the remaining ready nodes. Also, in case of the ratio of red pebbled in-neighbors, the ratio for source nodes can be interpreted as either 0 or 1, as desired.

Given the selected next-goal nodes, we assume that all processors compute these nodes concurrently. Processors can then execute an arbitrary amount of steps before this computation step, in order to ensure that in-neighbors of the next-goal node are available on the processor: at any point in the schedule before computing the next-goal node, they can load any node from slow memory, save any node to slow memory, delete any pebbles to save up space, or even recompute any node(s) that were previously computed on the same processor. That is, the strategy only defines the next new node to be computed by each processor, in a greedy manner, but the strategy is free to decide what I/O steps are executed (and when) in order to achieve this, which data values are kept in (or removed from) fast memory, and which data values are obtained by recomputation; as such, it covers a rather general class of greedy methods. Nonetheless, this simple restriction on the greedy selection of the next node to compute is already enough to show our lower bounds, i.e., that any strategy in this class can be rather far from the optimum.

## **B.2.1** Lemma 4: lower bound of $\frac{\Delta_{in}-1}{2}$

For the first claim in Lemma 4, we need to execute two modifications on the zipper gadget of Figure 2. On the one hand, we take two copies of this DAG. On the other hand, we replace the input groups by two gadgets that misguide the greedy heuristic, to ensure that our k = 2 processors will start working independently on the two copies.

More specifically, let  $u_1, ..., u_d, u_{d+1}, ..., u_{2d}$  denote the nodes in the input groups (with  $u_1, ..., u_d$  in the first, and  $u_{d+1}, ..., u_{2d}$  in the second). We still attach a chain of length 2g in front of each of these 2d nodes as before, in order to ensure that it is not beneficial to recompute them. For all  $i \in [2d-1]$ , we also add a further outgoing edge from  $u_i$  to the first node of the chain attached to  $u_{i+1}$ .

This ensures that in both copies, there is only a single topological ordering of the input group gadgets, which goes through the 2d chains consecutively, following each from front to end. In the greedy algorithm, the two processors will follow this in a parallel fashion for the two copies: in the first step, there are only two source nodes to compute, and after this, the next node in this order will always already have a red pebble of the given processor on (at least) one of its predecessors. If the greedy algorithm is sophisticated enough, then this process requires no I/O, apart from possibly saving the  $u_i$  to slow memory for future use. In any case, after  $(2g + 1) \cdot 2d$  computation steps (and a cost of O(1)), both processors have a red pebble on  $u_{2d}$ .

Assume that the first nodes of the main chains have incoming edges from the second input group (nodes  $u_{d+1}, ..., u_{2d}$ ) as in Figure 2. This means that after computing the input groups, the corresponding processors will have a red pebble on an in-neighbor  $u_{2d}$  of the first main chain node (in both copies), so this is the node that is computed next by each processor. From here, the processors will continue

processing the two main chains independently, since in each step, the next node in the main chain has an immediate predecessor (the previous node in the main chain) that already has a red pebble of the corresponding processor, and no red pebbles of the other processor. For r = d + 2, even if the input groups are loaded from slow memory for each main chain node (which is the lowest-cost solution), this results in an I/O cost of d for each node of the main chain, and a total cost of  $\frac{n}{2} \cdot (1 + d \cdot g) - O(1)$ altogether.